描述

AFE5851为模拟前端定位,其中功率和集成的水平是关键的应用。该器件包含16个可变增益放大器(VGA),后面跟着一个八进制高速(高达65 MSPS)模拟到数字转换器(ADC)。

每16个单端输入缓冲,接受多达1VPP最大输入摆幅,其后面是从-5dB到31分贝增益范围VGA。 VGA增益是数字控制的,并随时间变化的增益曲线可以被存储在存储器中,使用串行接口的设备内集成。

(在7.5,10或14MHz带衰减3dB)的可选择的夹紧和抗混叠低通滤波器也被集成在VGA和ADC每个通道之间。在VGA /抗混叠滤波器的输出是差分(限2 VPP)和驱动器,在两条的VGA之间共享,以优化功耗板上12位65MSPS的ADC。在交替的时钟周期,每个VGA输出进行采样,使有效采样频率为输入时钟速率的一半。该ADC还按比例降低其功耗要更低的采样率进行选择。

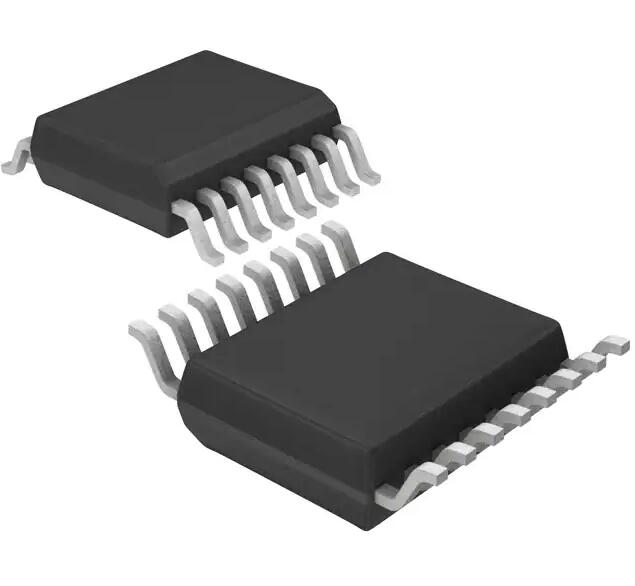

该ADC输出在LVDS被序列化流进一步降低功耗和电路板面积。该AFE5851是采用64引脚QFN封装(9x9mm2),并在整个工业温度范围(-40°C至85°C)

特性

Ø 16可变增益放大器(VGA)

Ø 16个单端输入缓冲带1VPP最大摆幅

Ø 5.5nV/√Hz的VCA输入噪声(31分贝增益)。

Ø 可变增益-5dB到31分贝随着0.125分贝步骤

Ø 数字增益控制

Ø 3阶抗混叠滤波器具有可编程截止频率(7.5,10和14兆赫)。

Ø 模拟数字转换器(ADC)

Ø 八通道12位,65 MSPS

Ø 32.5 MSPS每个输入通道最高

Ø 2 VGA输出交替每个ADC采样

Ø 内部和外部引用支持

Ø 无需外部解耦所需的引用

Ø 串行LVDS输出

Ø 1.8V和3.3V电源

Ø 每通道39 mW的总功率达到325 MSPS

Ø 64 QFN封装(9毫米×9毫米)