产品介绍

描述

FIN1217和FIN1215可将21位宽并行LVTTL(低压TTL)数据转换为三个串行LVDS(低压差分信号)数据流。锁相传输时钟与数据流一起通过LVDS链路并行传输。在每个传输时钟周期内,采样并传输21位输入LVTTL数据。FIN1218和FIN1216接收这三个串行LVDS数据流并转换回21位LVTTL数据。表1为所提供的串并/并串转换器的摘要表。 对于FIN1217,在85MHz的传输时钟频率时,每个LVDS通道上以595Mbps的速率传输21位LVTTL数据。这些芯片组解决了与宽型高速TTL接口相关的EMI和线缆尺寸问题。

特性

低功耗

20 MHz到85 MHz移位时钟支持

接收器时钟输出具有50%占空比

约1.2V的±1V共模范围

窄总线减小了线缆尺寸和成本

高吞吐速率(最高可达1.785 Gbps)

每通道最高可达595 Mbps

内部PLL,无外部组件

兼容TIA/EIA-644规格

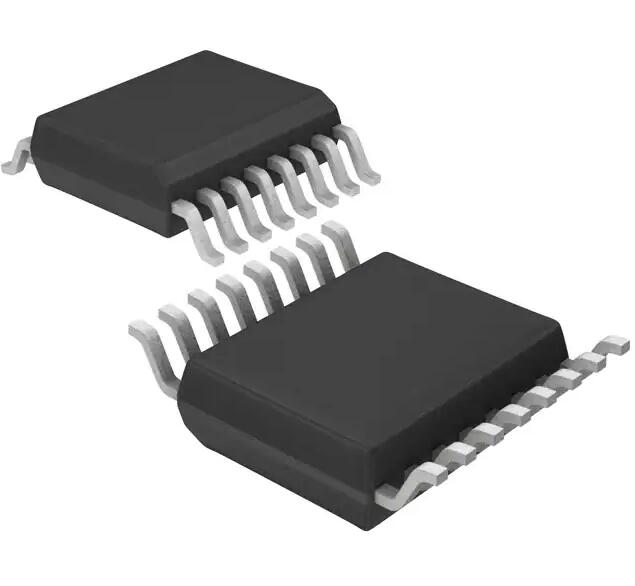

器件以48引线TSSOP封装提供

更多产品